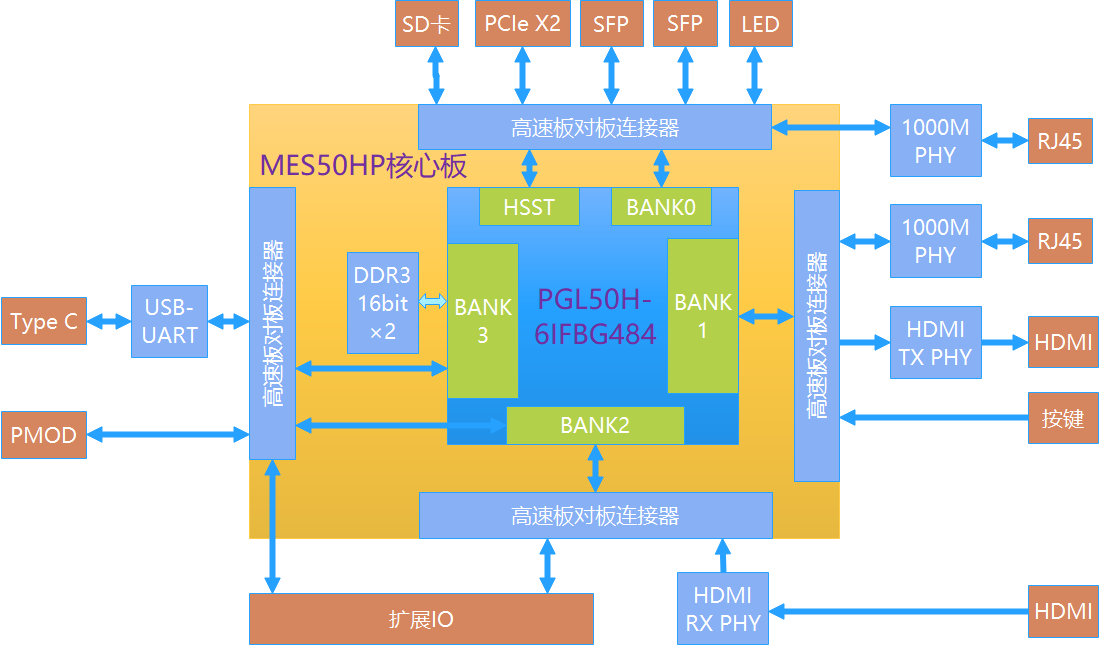

盘古-50开发板(MES50HP)采用了核心板+扩展板的结构,核心板与扩展板之间使用高速板对板连接器进行连接。

核心板主要由FPGA+2颗DDR3+Flash+电源及复位构成,承担了FPGA的最小系统运行及高速数据处理和存储的功能。

底板为核心板扩展了丰富的外围接口, 预留HDMI收发接口用于图像验证及处理;预留的光纤接口、10/100/1000M以太网接口,PCIE接口,方便各类高速通信系统验证;预留了一个40pin的IO扩展连接器,方便用户在开发平台基础上验证模块电路功能。

1个MES50HP核心板

1个MES50HP底板

1个12V电源适配器

1个Type-c数据线

开发板相关资料

MES50HP开发板资料v1

链接:https://pan.baidu.com/s/1iWtaUB7fLMtm54NuoTh9UA?pwd=emyv

提取码:emyv

活动时间

1. 申请报名:2023/03/16-2023/04/13

2. 公布名单:2023/04/14

3. 发货日期:2023/04/15(具体以实际发货日期为准)

4. 试用报告:截止至2023年5月16日

活动流程

1. 申请:点击免费申请按钮即可报名。请认真填写申请理由,展现有创意的试用计划和网络影响力,尽快完善论坛个人信息,这样可以大大提高申请通过几率哦~;

2. 筛选:网站根据申请者填写的试用计划和论坛活跃度两个维度进行筛选;

3. 名单公布:试用名单将在活动页公布;

4. 试用通知:名单公布后工作人员将以短信或电话的方式通知申请成功者,2天不回复算弃权;

5. 产品寄送:联系到试用者双方确认试用规则后,将产品快递给试用者;

6. 试用报告:收到货后试用开始,提交3篇试用报告文章和至少1个试用视频,试用报告要求100%原创,抄袭会被封杀哦;

7. 产品回收:请收到开发板的用户在规定时间内完成试用报告并上传至电子发烧友论坛,试用2个月时间后统一回收开发板。如发现未能按要求完成试用报告上传发布,将会提前要求您退回开发板。

试用报告要求

试用者收到试用套件后,进行学习评估,并在FPGA|CPLD|ASIC论坛发帖记录小眼睛科技紫光盘古50K开发板的试用过程,分享试用心得。

经过试用评测学习后,试用者使用小眼睛科技紫光盘古50K开发板并在论坛发帖记录项目过程、心得,提供文字+视频展示。

试用报告要求3篇试用报告+1个试用视频,内容可以包括:

1. 开箱评测(从功能特性、系统框图、硬件资源、做工、FPGA资源、功能演示等方面评测);

2. 各个接口模块使用过后的评测;

3. 开发板配套教程实验;

4. FPGA开发板试用过程中发现的技巧或经验;

5. 试用者独立设计的实验.....

报告形式:标题格式【小眼睛科技紫光盘古50K开发板试用体验】+自拟标题

注意事项

1.本次试用不进行拉票环节;

2.不按照要求完成试用者一经查实将拉黑处理;

3.有问题请联系电子发烧友工作人员(微信:elecfans_666);

4.若因突发状况,无法继续完成试用,以及收到套件的15天内,若没有更新内容,请主动退还套件至ElecFans(PS:运费自理),方便其他网友继续试用;

5.活动过程中,套件所有权归ElecFans,试用者只拥有套件使用权; 若在使用过程中出现恶意损坏开发套件的行为,请原价赔偿;

6.电子发烧友拥有最终解释权!

MYMINIEYE是一家专业的FPGA方案公司,擅长各类FPGA产品开发及项目落地。